Three-Phase Inverter Design Using Wide-Bandgap Semiconductors to Achieve High Power Density

### THREE-PHASE INVERTER DESIGN USING WIDE-BANDGAP SEMICONDUCTORS TO ACHIEVE HIGH POWER DENSITY

BY

WILLIAM MICHAEL EULL, B.Eng. & Mgmt.

A THESIS

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING AND THE SCHOOL OF GRADUATE STUDIES OF MCMASTER UNIVERSITY

IN PARTIAL FULFILMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

© Copyright by William Michael Eull, August 2016

All Rights Reserved

| Master of Applied Science (2016)    |

|-------------------------------------|

| (Electrical & Computer Engineering) |

McMaster University Hamilton, Ontario, Canada

| TITLE:      | Three-Phase Inverter Design Using Wide-Bandgap Semi- |

|-------------|------------------------------------------------------|

|             | conductors to Achieve High Power Density             |

|             |                                                      |

| AUTHOR:     | William Michael Eull                                 |

|             | B.Eng. & Mgmt. (Electrical Engineering)              |

|             | McMaster University, Hamilton, Canada                |

|             |                                                      |

| SUPERVISOR: | Dr. Ali Emadi                                        |

NUMBER OF PAGES: xiv, 172

To my family.

#### Abstract

Electric and more-electric vehicle proliferation continues unabated as government mandates worldwide demand fuel economies in excess of what conventional internal combustion engines are capable of. Vehicle electrification, to any degree, is perceived to be the means by which automotive companies may meet these targets. Electrification introduces a myriad of problems including cost, weight and reliability, all of which must be addressed in their own right. The rapid commercialisation of wide-bandgap semiconductor materials which, as a whole, exhibit properties superior to ubiquitous Silicon, provides the opportunity for power electronic converter minimisation and efficiency maximisation, easing the challenge of meeting current and incoming standards.

This thesis concerns itself with the design methodology of a highly power dense converter, as applied to a three-phase inverter. By using figures of merit, simple modelling techniques and novel discrete component selection tools, a well-designed converter is achieved that is capable of switching 30kW of electric power at 100kHz in a small package. Testing results show that the converter, with a simple forced air heatsinking solution, can effectively switch 15kW of power. Given the temperature rise of one phase leg of the inverter relative to the others, a superior heatsink design would allow the inverter to reach its rated power levels.

#### Acknowledgements

This research was undertaken, in part, thanks to funding from the Canada Excellence Research Chairs (CERC) Program.

I would like to graciously thank my supervisor, Dr. Ali Emadi, for providing me with the opportunity to pursue this research at the McMaster Automotive Resource Centre (MARC).

Special thanks go to my friend and unofficial co-supervisor Dr. Matthias Preindl for all his help and invaluable suggestions over the previous two years. His input directly shaped this work.

Je voudrais remercier Prof. Babak Nahid-Mobarakeh pour m'avoir donner la chance de faire un stage au laboratoire de la Groupe de Recherche en Électrotechnique et Électronique de Nancy (GREEN) à l'Université de Lorraine, Nancy, France. Ce fut des moments inoubliables pour moi.

Many thanks to the research engineers and post-doctoral fellows at MARC, particularly Drs. Berker Bilgin and Pierre Magne, for their guidance in industry projects that enabled me to develop and refine skills utilised within this thesis.

I am indebted to James, Hao and Yingguang for the kind help they provided me: James for helping with the design of figures throughout this document; and Hao and Yingguang for helping me obtain experimental results. Your selflessness is humbling. And, of course, thank you to all my friends, new and old, who directly and indirectly helped me as I pursued this degree. The value of your support and friendship cannot be explained by words alone.

### Contents

| - | Abstra | act     |                                                   | iii |

|---|--------|---------|---------------------------------------------------|-----|

| - | Ackno  | wledge  | ements                                            | iv  |

|   | 1 Int  | roduct  | ion                                               | 1   |

|   | 2 Swi  | itching | Devices & Comparative Analysis                    | 14  |

|   | 2.1    | Types   | s of Devices                                      | 14  |

|   |        | 2.1.1   | Bipolar Junction Transistor                       | 14  |

|   |        | 2.1.2   | Metal-Oxide-Semiconductor Field-Effect Transistor | 17  |

|   |        | 2.1.3   | Insulated-Gate Bipolar Transistor                 | 21  |

|   |        | 2.1.4   | Hybrid Silicon                                    | 22  |

|   |        | 2.1.5   | Diodes                                            | 24  |

|   | 2.2    | Why     | Consider Wide-Bandgap Materials?                  | 25  |

|   | 2.3    | Types   | s of Semiconductor Materials                      | 27  |

|   |        | 2.3.1   | Silicon                                           | 27  |

|   |        | 2.3.2   | Silicon Carbide                                   | 28  |

|   |        | 2.3.3   | Gallium Nitride                                   | 29  |

|   |        | 2.3.4   | Gallium Arsenide                                  | 30  |

|   |      | 2.3.5   | Examples                                | 31 |

|---|------|---------|-----------------------------------------|----|

|   |      | 2.3.6   | Conclusions                             | 35 |

|   | 2.4  | Mater   | ial Figures of Merit                    | 36 |

|   |      | 2.4.1   | Johnson's Figure of Merit               | 36 |

|   |      | 2.4.2   | Baliga's Figure of Merit                | 37 |

|   |      | 2.4.3   | Baliga's High Frequency Figure of Merit | 37 |

|   |      | 2.4.4   | New High Frequency Figure of Merit      | 38 |

|   |      | 2.4.5   | Huang's Chip Area Figure of Merit       | 39 |

|   |      | 2.4.6   | Summary                                 | 40 |

|   | 2.5  | Device  | e-Specific Figures of Merit             | 40 |

|   |      | 2.5.1   | Baliga's High Frequency Figure of Merit | 40 |

|   |      | 2.5.2   | New High Frequency Figure of Merit      | 41 |

|   |      | 2.5.3   | Power Density Figures of Merit          | 41 |

|   |      | 2.5.4   | MOSFET Figure of Merit                  | 42 |

|   |      | 2.5.5   | IGBT Figure of Merit                    | 43 |

|   | 2.6  | Summ    | ary                                     | 43 |

| 3 | Inve | erter N | Iodelling and Analysis                  | 45 |

|   | 3.1  | Switch  | n Modelling Techniques                  | 45 |

|   |      | 3.1.1   | Simulation                              | 46 |

|   |      | 3.1.2   | Analytical                              | 46 |

|   |      | 3.1.3   | Testing                                 | 56 |

|   |      | 3.1.4   | Conclusions                             | 58 |

|   | 3.2  | Three-  | Phase Inverter Modelling                | 59 |

|   |      | 3.2.1   | Sinusoidal Pulse Width Modulation       | 59 |

|   | 3.3               | Conve                                                                  | erter Loss Estimation                                                                                                                                                                                                                                                                                        | 64                                           |

|---|-------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|   | 3.4               | Power                                                                  | Electronic Converter Optimisation                                                                                                                                                                                                                                                                            | 71                                           |

|   |                   | 3.4.1                                                                  | Convex Optimisation                                                                                                                                                                                                                                                                                          | 71                                           |

|   |                   | 3.4.2                                                                  | Heuristic Optimisation                                                                                                                                                                                                                                                                                       | 76                                           |

|   |                   | 3.4.3                                                                  | Pseudo-Optimality                                                                                                                                                                                                                                                                                            | 82                                           |

|   | 3.5               | Parasi                                                                 | itics Analysis                                                                                                                                                                                                                                                                                               | 82                                           |

|   |                   | 3.5.1                                                                  | Current Density                                                                                                                                                                                                                                                                                              | 83                                           |

|   |                   | 3.5.2                                                                  | Resistance                                                                                                                                                                                                                                                                                                   | 88                                           |

|   |                   | 3.5.3                                                                  | Inductance                                                                                                                                                                                                                                                                                                   | 90                                           |

|   |                   | 3.5.4                                                                  | Capacitance                                                                                                                                                                                                                                                                                                  | 91                                           |

|   |                   | 3.5.5                                                                  | Parasitic Interactions                                                                                                                                                                                                                                                                                       | 92                                           |

|   | 3.6               | Summ                                                                   | nary                                                                                                                                                                                                                                                                                                         | 94                                           |

|   |                   |                                                                        |                                                                                                                                                                                                                                                                                                              |                                              |

| 4 | Hig               | h Pow                                                                  | er Density Inverter Design                                                                                                                                                                                                                                                                                   | 95                                           |

| 4 | <b>Hig</b><br>4.1 |                                                                        | , j                                                                                                                                                                                                                                                                                                          | <b>95</b><br>96                              |

| 4 | Ū                 | Power                                                                  | Density                                                                                                                                                                                                                                                                                                      |                                              |

| 4 | 4.1               | Power                                                                  | Density     9       nes     9                                                                                                                                                                                                                                                                                | 96                                           |

| 4 | 4.1               | Power<br>Switch                                                        | Density       9         nes       9         Device Figures of Merit       9                                                                                                                                                                                                                                  | 96<br>97                                     |

| 4 | 4.1               | Power<br>Switch<br>4.2.1                                               | Density       9         nes       9         Device Figures of Merit       9         Linear Analysis of Devices       9                                                                                                                                                                                       | 96<br>97<br>97                               |

| 4 | 4.1               | Power<br>Switch<br>4.2.1<br>4.2.2<br>4.2.3                             | Density       9         nes       9         Device Figures of Merit       9         Linear Analysis of Devices       9         Silicon Carbide Switches       10                                                                                                                                             | 96<br>97<br>97<br>98                         |

| 4 | 4.1               | Power<br>Switch<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                    | Density       9         nes       9         Device Figures of Merit       9         Linear Analysis of Devices       9         Silicon Carbide Switches       10         Chosen Switch       10                                                                                                              | 96<br>97<br>97<br>98<br>02                   |

| 4 | 4.1<br>4.2        | Power<br>Switch<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                    | Density       9         nes       9         Device Figures of Merit       9         Linear Analysis of Devices       9         Silicon Carbide Switches       10         Chosen Switch       10         nek Capacitor       10                                                                               | 96<br>97<br>97<br>98<br>02<br>04             |

| 4 | 4.1<br>4.2        | Power<br>Switch<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>DC-lin          | Density       9         nes       9         Device Figures of Merit       9         Linear Analysis of Devices       9         Silicon Carbide Switches       10         Chosen Switch       10         nk Capacitor       10         Optimality in Selection       10                                       | 96<br>97<br>97<br>98<br>02<br>04<br>05       |

| 4 | 4.1<br>4.2        | Power<br>Switch<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>DC-lin<br>4.3.1 | Density       9         nes       9         Device Figures of Merit       9         Linear Analysis of Devices       9         Silicon Carbide Switches       9         Chosen Switch       10         nk Capacitor       10         Optimality in Selection       10         Capacitor Bank Design       10 | 96<br>97<br>97<br>98<br>02<br>04<br>05<br>05 |

|   |     | 4.3.5   | Conclusions                           | 124 |

|---|-----|---------|---------------------------------------|-----|

|   | 4.4 | PCB     |                                       | 126 |

|   | 4.5 | Summ    | ary                                   | 129 |

| 5 | Inv | erter F | Prototype & Experimental Results      | 130 |

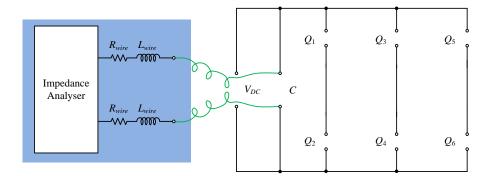

|   | 5.1 | Parasi  | tic Parameters                        | 130 |

|   |     | 5.1.1   | Measurement Preparation               | 131 |

|   |     | 5.1.2   | DC-link Capacitor                     | 132 |

|   |     | 5.1.3   | MOSFET                                | 132 |

|   |     | 5.1.4   | PCB Capacitance                       | 136 |

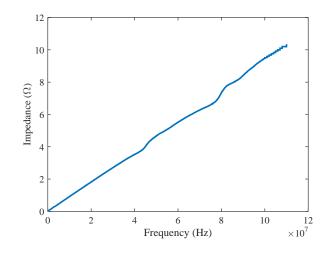

|   |     | 5.1.5   | Commutation Loop Impedance            | 137 |

|   |     | 5.1.6   | Output Stage Impedance                | 143 |

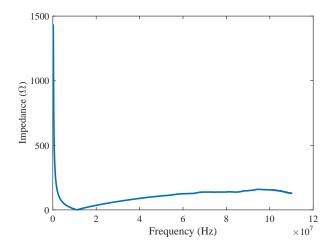

|   |     | 5.1.7   | Assembled PCB                         | 144 |

|   |     | 5.1.8   | Conclusions                           | 147 |

|   | 5.2 | Low F   | Power PMSM Configuration              | 147 |

|   | 5.3 | High l  | Power Induction Machine Configuration | 149 |

|   | 5.4 | Summ    | ary                                   | 154 |

| 6 | Cor | nclusio | ns & Future Work                      | 159 |

|   | 6.1 | Conclu  | usions                                | 159 |

|   | 6.2 | Future  | e Work                                | 161 |

## List of Figures

| 1.1 | Electrified vehicle architectures, with battery charging circuit (Emadi,                                                                            |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | 2015)                                                                                                                                               | 3  |

| 1.2 | Electric power flow and conversion chain in an electrified vehicle (Bilgin                                                                          |    |

|     | et al., 2015)                                                                                                                                       | 4  |

| 2.1 | BJT schematic with parasitic capacitances.                                                                                                          | 15 |

| 2.2 | BJT current-voltage characteristic.                                                                                                                 | 16 |

| 2.3 | MOSFET current-voltage characteristic.                                                                                                              | 18 |

| 2.4 | MOSFET schematic with parasitic capacitances                                                                                                        | 20 |

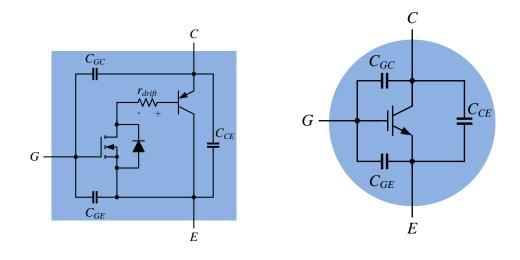

| 2.5 | Complex and basic IGBT schematics.                                                                                                                  | 21 |

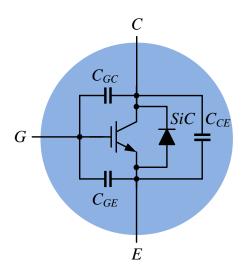

| 2.6 | Hybrid IGBT schematic with parasitic capacitances                                                                                                   | 23 |

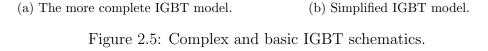

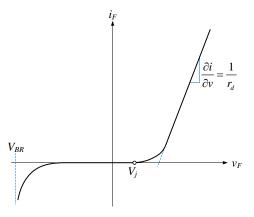

| 2.7 | Current-voltage characteristic of a generic diode                                                                                                   | 24 |

| 2.8 | DC capacitors of different types, voltages and capacitances: (a) 400V,                                                                              |    |

|     | $500\mu\mathrm{F},\mathrm{film};\mathrm{(b)}$ 63V, $1000\mu\mathrm{F},\mathrm{electrolytic};\mathrm{and}$ (c) 800V, $5\mu\mathrm{F},\mathrm{film}.$ | 26 |

| 3.1 | Linearised inductive switching model waveforms                                                                                                      | 47 |

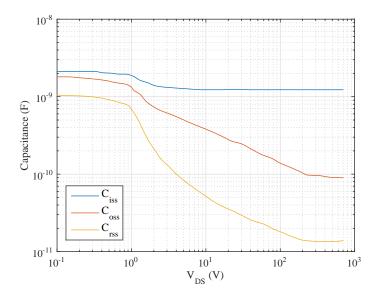

| 3.2 | Parasitic capacitances of SCT2120AF Silicon Carbide MOSFET                                                                                          | 49 |

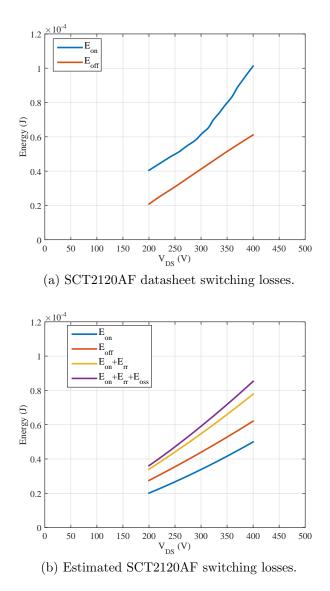

| 3.3 | Datasheet and estimated switching losses of SCT2120AF MOSFET                                                                                        | 52 |

| 3.4 | Model of a MOSFET with all major parasitics included.                                                                                               | 54 |

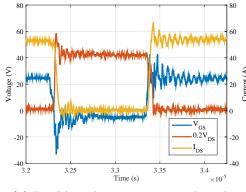

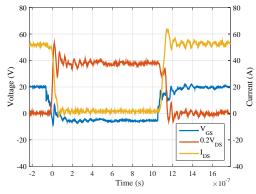

| 3.5  | Double pulse test waveforms with $V_{DC} = 200$ V and $I_{DS} = 50$ A on two |     |

|------|------------------------------------------------------------------------------|-----|

|      | different test platforms                                                     | 57  |

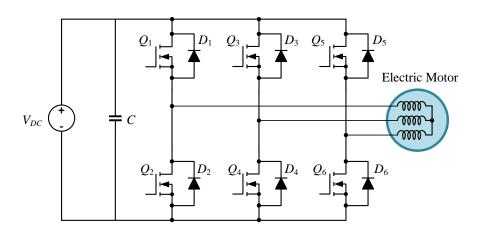

| 3.6  | Three-phase inverter schematic.                                              | 59  |

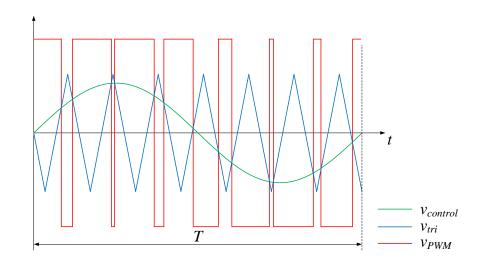

| 3.7  | Sinusoidal Pulse Width Modulation.                                           | 60  |

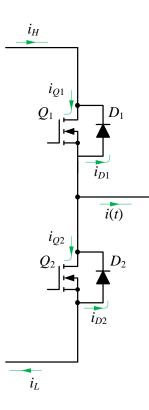

| 3.8  | Single phase leg analysis of a three-phase inverter under SPWM               | 61  |

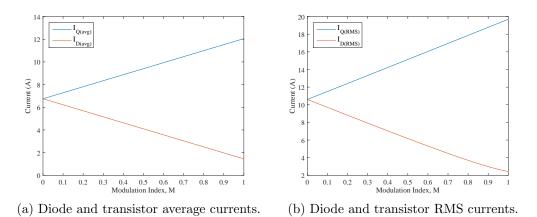

| 3.9  | Sweep of the modulation index under SPWM with $\cos \phi = 1$ and            |     |

|      | $I_{o,RMS} = 30A.$                                                           | 64  |

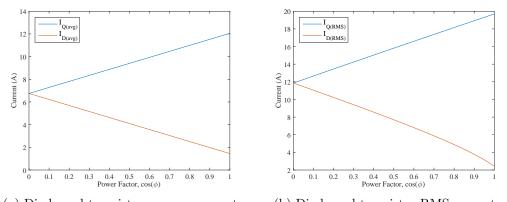

| 3.10 | Sweep of the power factor under SPWM with $M = 1$ and $I_{o,RMS} = 30A$ .    | 64  |

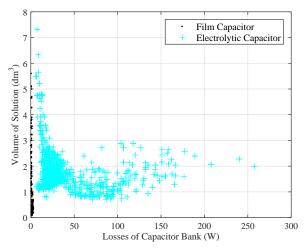

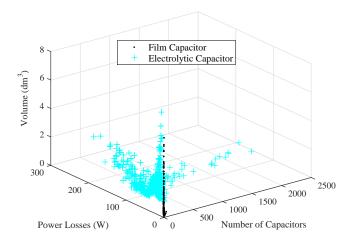

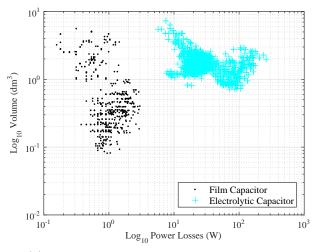

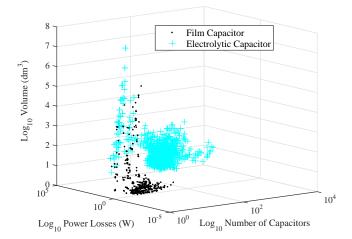

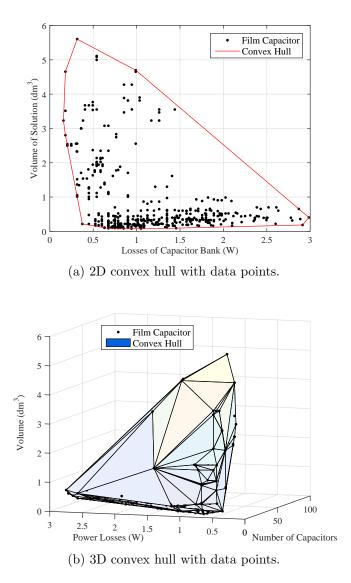

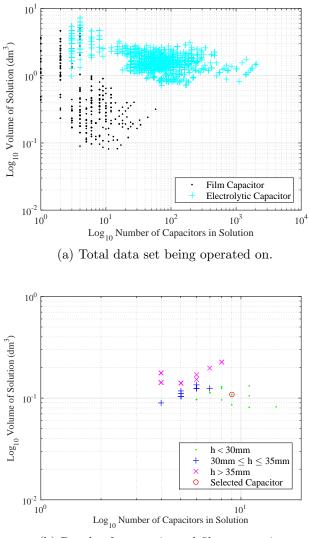

| 3.11 | 2D and 3D plots illustrating non-convex, random nature of data               | 72  |

| 3.12 | Log-log plots of the data presented in Figure 3.11                           | 73  |

| 3.13 | 2D and 3D plots illustrating the convex hull on a reduced dataset shown      |     |

|      | in Figure 3.11                                                               | 77  |

| 3.14 | Ten runs of the simulated annealing algorithm on the test function           |     |

|      | with different initial temperatures.                                         | 81  |

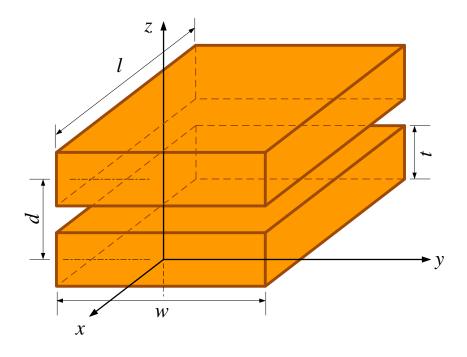

| 3.15 | Reference drawing of parallel conductors with dimension notations            | 84  |

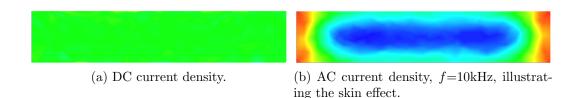

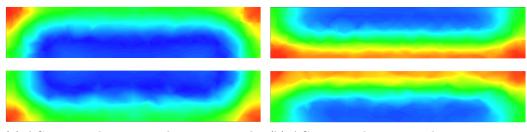

| 3.16 | DC current density of a copper bus bar.                                      | 85  |

| 3.17 | DC and AC current densities on a copper transmission line with a             |     |

|      | width and thickness of 10 and 2mm, respectively.                             | 86  |

| 3.18 | AC current densities illustrating the proximity effect on a copper trans-    |     |

|      | mission line with a width, thickness and separation of $10, 2$ and $0.5$ mm, |     |

|      | respectively.                                                                | 87  |

| 3.19 | AC current density of a copper bus bar with $f_s=10$ kHz                     | 88  |

| 4.1  | Linear analysis applied to the switches in Table 4.2 with a DC-link          |     |

|      | voltage of 400V.                                                             | 100 |

| 4.2  | Linear analysis applied to the switches in Table 4.3 with a DC-link   |     |

|------|-----------------------------------------------------------------------|-----|

|      | voltage of 800V                                                       | 101 |

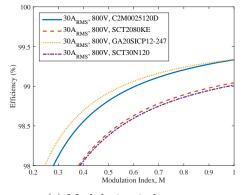

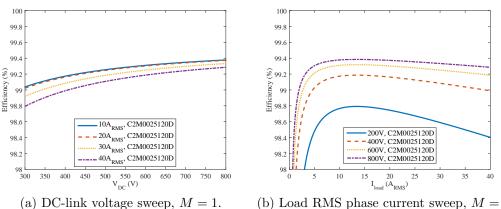

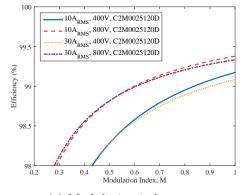

| 4.3  | Silicon Carbide MOSFET efficiency maps with a switching frequency     |     |

|      | of 100kHz and unity power factor                                      | 103 |

| 4.4  | Cree $C2M0025120D$ efficiency maps with a switching frequency of      |     |

|      | 100kHz and unity power factor.                                        | 104 |

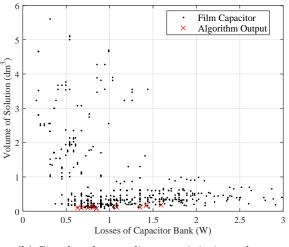

| 4.5  | Single-objective and multi-objective minimum value searches using the |     |

|      | brute force algorithm.                                                | 112 |

| 4.6  | Constrain and filter operation, reducing the dataset from 2000 to 40  |     |

|      | items                                                                 | 115 |

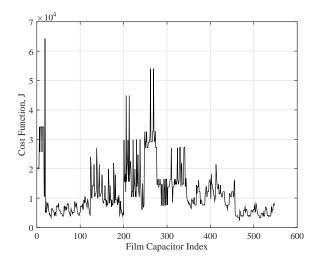

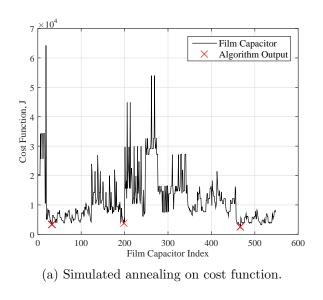

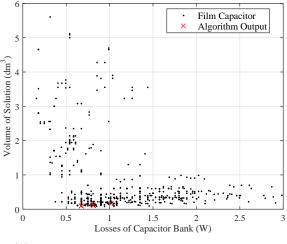

| 4.7  | Cost function output given the film capacitor data.                   | 116 |

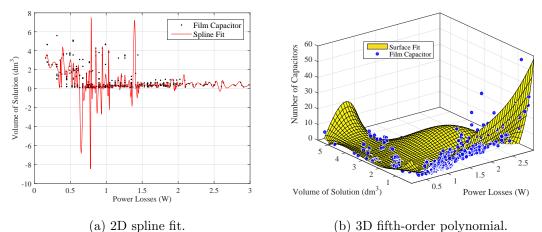

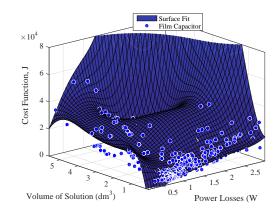

| 4.8  | MATLAB curve fitting toolbox surface fits and the underlying data     | 118 |

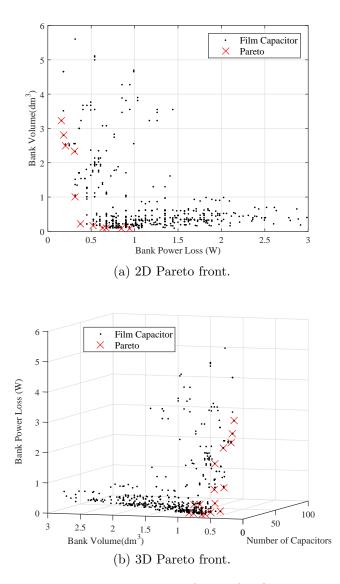

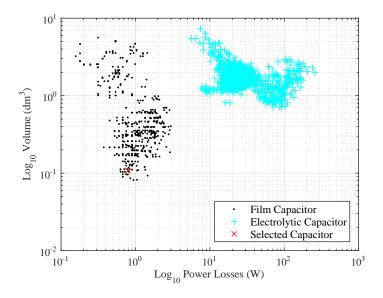

| 4.9  | 2D and 3D Pareto fronts for film capacitors                           | 120 |

| 4.10 | Ten runs of simulated annealing algorithm on dataset                  | 121 |

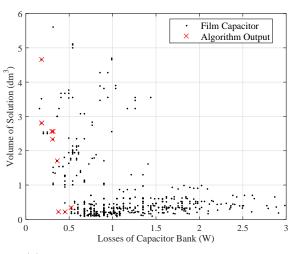

| 4.11 | Results of ten runs of the simulated annealing algorithm on the cost  |     |

|      | function                                                              | 122 |

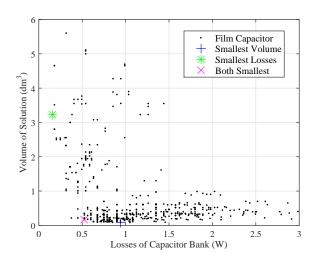

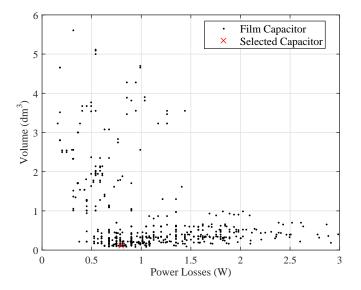

| 4.12 | Entire data set with selected capacitor denoted                       | 125 |

| 4.13 | Film capacitor only dataset with chosen capacitor denoted             | 125 |

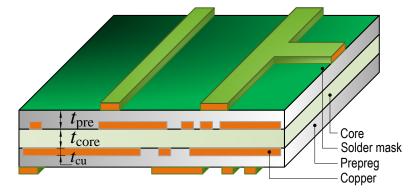

| 4.14 | Prototypical four-layer PCB stackup                                   | 127 |

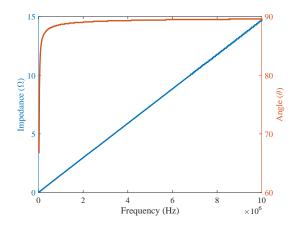

| 5.1  | An example magnitude and phase characteristic for a wire              | 131 |

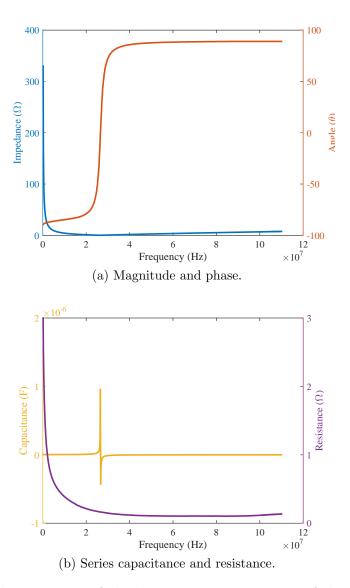

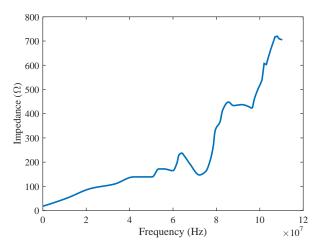

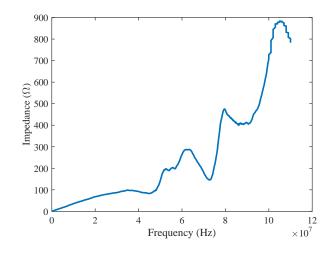

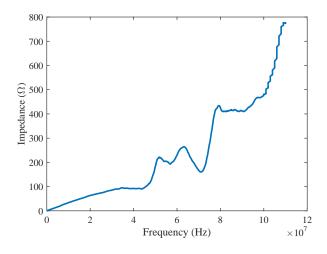

| 5.2  | Impedance curves of the DC-link capacitor $B32774D8505K$              | 132 |

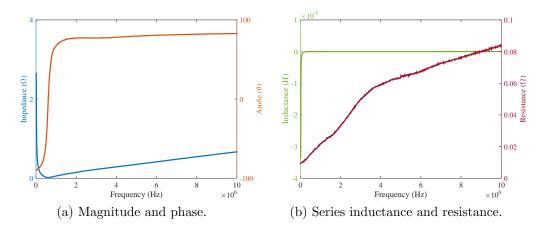

| 5.3  | Impedance curves of the gate-drain connection of the Silicon Carbide  |     |

|      | MOSFET <i>C2M0025120D</i>                                             | 133 |

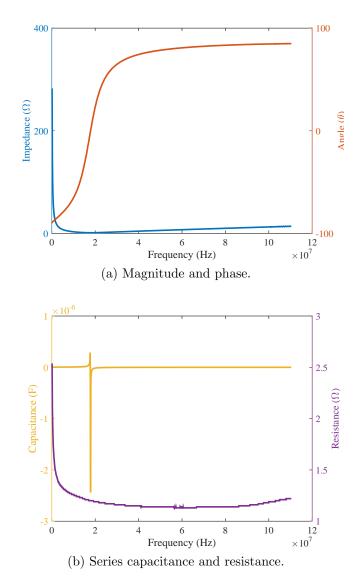

| 5.4  | Impedance curves of the gate-source connection of the Silicon Carbide  |     |

|------|------------------------------------------------------------------------|-----|

|      | MOSFET <i>C2M0025120D</i>                                              | 134 |

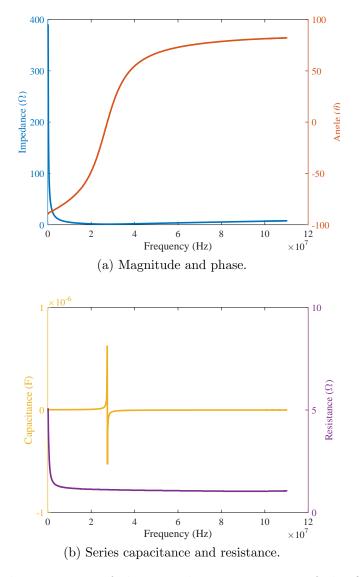

| 5.5  | Impedance curves of the drain-source connection of the Silicon Carbide |     |

|      | MOSFET <i>C2M0025120D</i> when off                                     | 135 |

| 5.6  | Impedance curve of the gate-source connection of the Silicon Carbide   |     |

|      | MOSFET <i>C2M0025120D</i> when on                                      | 136 |

| 5.7  | PCB capacitance measurement schematic.                                 | 136 |

| 5.8  | Impedance curve of the PCB alone when measuring from the positive      |     |

|      | terminal of capacitor 1 to the negative terminal of capacitor 9        | 137 |

| 5.9  | PCB impedance measurement schematic short circuiting the capacitors.   | 138 |

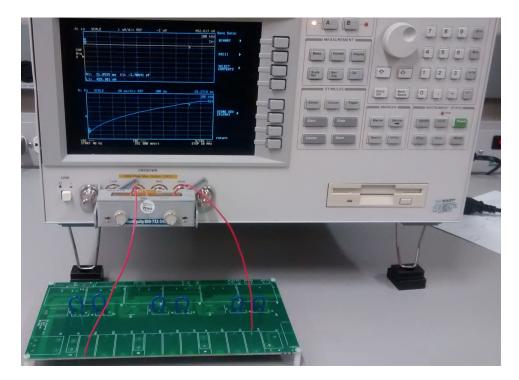

| 5.10 | Physical measurement setup for the commutation loop with the capac-    |     |

|      | itors shorted.                                                         | 139 |

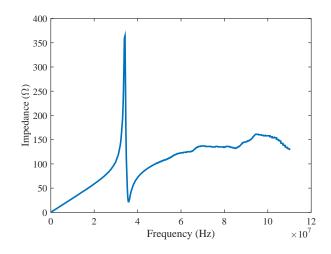

| 5.11 | Impedance curve of the commutation loop from the transistor terminals. | 139 |

| 5.12 | PCB impedance measurement schematic short circuiting the phase legs.   | 140 |

| 5.13 | A test of the commutation loop with the transistor phases shorted.     | 141 |

| 5.14 | Impedance curve of the commutation loop from the capacitor termi-      |     |

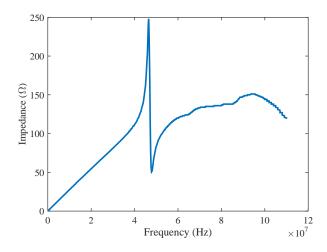

|      | nals, phase A short circuited.                                         | 142 |

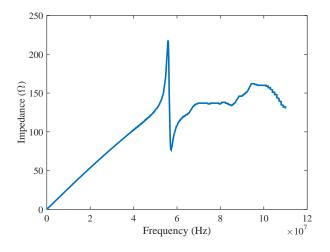

| 5.15 | Impedance curve of the commutation loop from the capacitor termi-      |     |

|      | nals, phases A and B short circuited                                   | 142 |

| 5.16 | Impedance curve of the commutation loop from the capacitor termi-      |     |

|      | nals, phases A, B and C short circuited.                               | 143 |

| 5.17 | PCB impedance measurement schematic measuring the output stage.        | 143 |

| 5.18 | Impedance curve of the output stage of phase A                         | 144 |

| 5.19 | PCB impedance measurement schematic for an assembled inverter.         | 144 |

| 5.20 | Impedance curve of the assembled PCB, all transistors off               | 145 |

|------|-------------------------------------------------------------------------|-----|

| 5.21 | Impedance curve of the assembled PCB, phase leg A on                    | 145 |

| 5.22 | Impedance curve of the assembled PCB, phase legs A and B on             | 146 |

| 5.23 | Impedance curve of the assembled PCB, phase legs A, B and C on          | 146 |

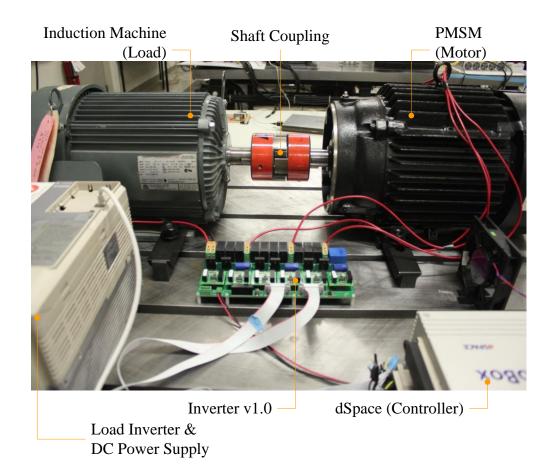

| 5.24 | Full testing setup of inverter version 1.0.                             | 148 |

| 5.25 | Comparison between model and measurements at a DC-link voltage of       |     |

|      | 300V and a switching frequency of 10kHz.                                | 149 |

| 5.26 | Inverter version 1.1.                                                   | 150 |

| 5.27 | Testing setup of inverter version 1.1.                                  | 151 |

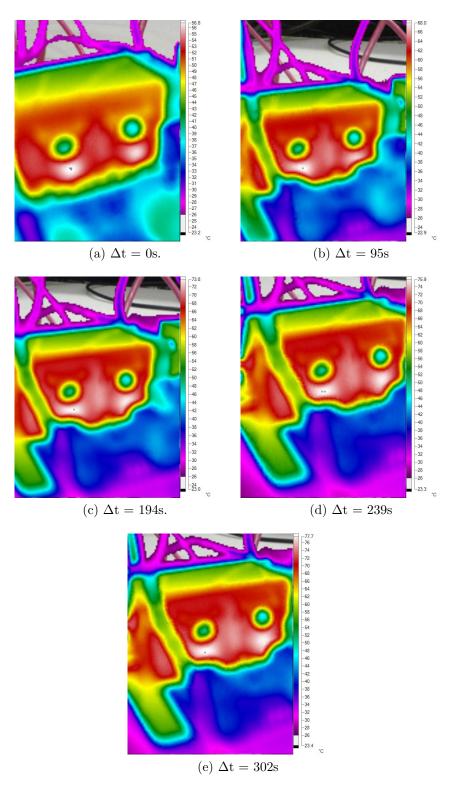

| 5.28 | MOSFET case hotspot temperatures over time, relative to the first       |     |

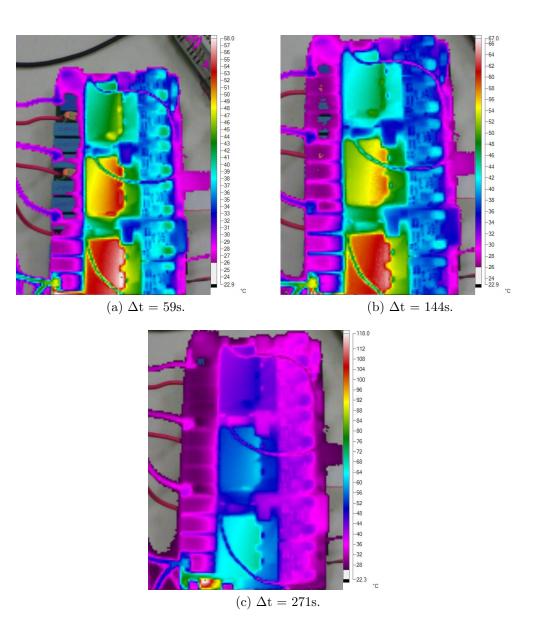

|      | measurement.                                                            | 153 |

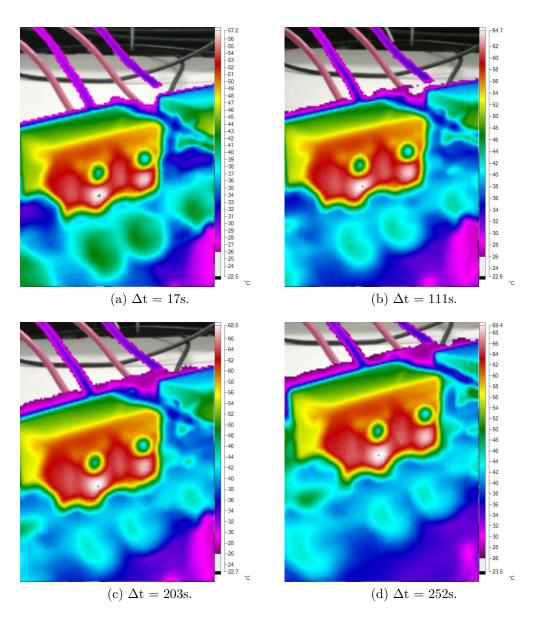

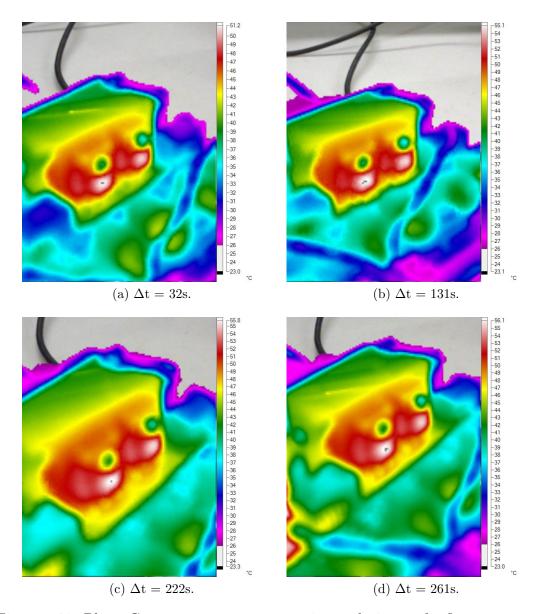

| 5.29 | Phase A case temperatures over time, relative to the first measurement  | 155 |

| 5.30 | Phase B case temperatures over time, relative to the first measurement. | 156 |

| 5.31 | Phase C case temperatures over time, relative to the first measurement  | 157 |

| 5.32 | Heatsink temperatures over time, relative to the first measurement.     | 158 |

### Chapter 1

### Introduction

With transportation alone contributing to a third of green house gas emissions in the United States, a paradigm shift is required to slow the onset and minimise the impact of climate change. Governments worldwide are beginning to recognise the economic and societal impacts of air pollution and climate change and have been introducing stricter fuel economy mandates for new vehicles. These, in tandem with the general public's demand for more environmentally friendly transportation options, have been driving an increase in interest in electrified vehicles by automotive manufacturers (Bilgin *et al.*, 2015).

One of the most notable programs for mandated vehicle electrification is California's Zero Emission Vehicle (ZEV) program. Devised in 1990 and launched in 1998, the ZEV program mandates that a certain percentage of new car sales in the state must output no pollution when driving, encompassing fuel cell (FC) and batteryelectric vehicles (BEVs). Other states have opted for similar programs following the successful launch in California (Alliance of Automobile Manufacturers, 2016).

Another program launched by the United States Department of Energy is the

*EV Everywhere Challenge*, which is a collaborative project between manufacturers, national laboratories and the government to innovate in transportation electrification to obtain size and cost reductions. Targets are laid out for cost, power density and other key parameters in powertrain development in the coming years (Rogers, 2012). New developments and technologies are key to achieving these mandates and targets.

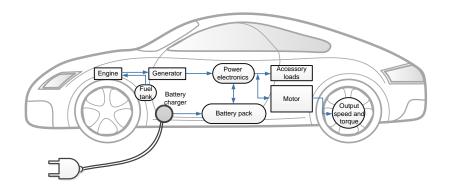

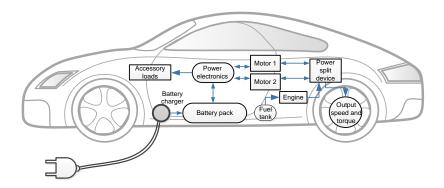

Three major electric vehicle architectures exist and are shown in Figures 1.1. Automotive manufacturers develop a powertrain based off of what architecture meshes best with their planned vehicle and load profiles. Vehicle types can be broken in to three major categories: hybrid electric (HEV), battery electric and fuel cell. Hybrids can be further subdivided depending on the level of hybridisation, with the lowest level being a start-stop configuration and the highest a plug-in hybrid vehicle, where the battery is the primary propulsion source and gasoline the secondary. More comprehensive illustrations of electrified vehicle architectures with many of the auxiliary loads shown can be found in (Emadi *et al.*, 2006).

(a) Series configuration.

(b) Parallel configuration.

(c) Compound configuration.

Figure 1.1: Electrified vehicle architectures, with battery charging circuit (Emadi, 2015).

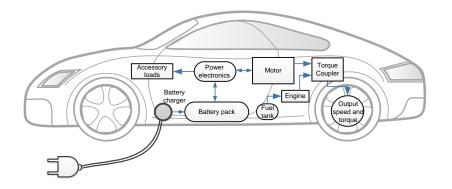

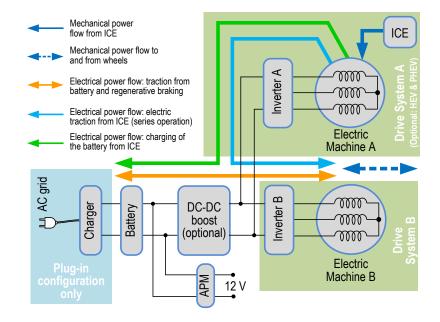

A simplified power conversion chain in an electrified vehicle is presented in Figure 1.2. The battery does not connect to the motor directly for two reasons: the first is that a battery's output is DC and AC motors are better suited for vehicle applications; and the second is that a high voltage battery pack is expensive to build and manage charge balancing due to the need to create large series stacks to increase the voltage level. For these reasons, two converters interface between the battery and the electric motor: a DC/DC converter where current can flow to the motor and back to the battery, and an inverter to convert from DC to AC. The battery also connects to an auxiliary power module (APM) to bring the voltage level down to that which auxiliary loads demand. If the vehicle is a PHEV or BEV, then a battery charging circuit is required; if not, it is omitted.

Figure 1.2: Electric power flow and conversion chain in an electrified vehicle (Bilgin *et al.*, 2015).

For illustration's sake, inverter A is assumed to not be active. The efficiency in the primary power conversion chain, from battery to motor, is the product of the efficiencies of the components in series and is calculated as (1.1). For a high chain efficiency, each individual item needs to have a high efficiency.

$$\eta_{drive} = \eta_{battery} \eta_{DC/DC} \eta_{invB} \eta_{motor} \tag{1.1}$$

It is here where the benefits of novel technologies for power switches can be best observed. Silicon, the material underpinning the modern technological revolution and the majority of power converters presently, is approaching its limits and it takes innovations, such as Superjunction technology, to obtain ever higher performance. Widebandgap (WBG) materials, however, have intrinsic properties that are favourable to reducing power losses, making them capable of higher efficiency operation.

As outlined, there are three, four or more–depending on the vehicle's architecture (Emadi *et al.*, 2008)–major power converters in an electric vehicle. They all stand to benefit, in some form, from a shift to wide-bandgap materials. Due to differences in voltage and current levels, some materials are more likely to see use than others for a given converter.

The auxiliary power module (APM) steps down the battery voltage, high or low, to 12V, replacing the alternator for powering auxiliary loads. There exist many possible circuit topologies and control schemes for an APM (Hou *et al.*, 2015). Inductors or transformers, depending on whether isolation is desired, are required and can be made smaller by increasing the switching frequency. On the low voltage bus, the currents can be in the hundreds of Amperes, demanding switches with low conduction losses. Wide-bandgap devices can meet both of these needs..

The bidirectional boost converter steps up the voltage from the battery to levels that would generate a desired speed for the electric motor, as well stepping-down voltage during a regenerative braking operation to recharge the battery a small amount. There are several topologies, primarily related to the number of switches and inductors in the system. A phase can be defined as a conduction leg with two switches, for forward and reverse conduction. Topology variations can have one inductor per phase, a shared inductor between phases, or some variant thereof (Ye *et al.*, 2014a). Higher phase numbers are beneficial for reducing the volume of the required inductor, as well as the power losses in the switches. In one study, the benefits to be seen in terms of inductor and switch volume and losses were quantified, justifying a decision to move to a higher phase order (Magne *et al.*, 2015). Increasing the switching frequency can further reduce inductor volume, thereby driving upwards the power density of the converter. WBG semiconductor devices are capable of switching at a higher frequency than their Silicon counterparts with lower losses, providing a viable avenue to reduce the inductor volume and even the heatsink via reduced losses.

The inverter converts the stepped-up DC voltage to an AC voltage, which is used to drive the electric motor. Many inverter topologies exist, such as the Z-source (ZSI), current source (CSI), voltage source (VSI) and various multi-level inverters. These topologies can exist as a single three-phase inverter or several in parallel for supplying several loads. The ease by which a voltage source inverter may be implemented, as well as the reduction in the total number of components relative to other topologies, make it preferred for automotive applications (Ye *et al.*, 2012b). Cost considerations come in to play for these more component-heavy topologies, which spurred an investigation in to alternative, reduced-part dual inverters. The general findings were that for a dual inverter, reliability and voltage utilisation issues make it difficult to justify a reduction in transistors (Ye *et al.*, 2012a). Outside of component count reduction, the other means by which the size of an inverter can be reduced is the DC capacitor bank, which is estimated to consume 35% and 23% of the volume and weight, respectively (Balachandran *et al.*, 2014), of a traction inverter. Fast switching devices reduce the capacitance required for a given voltage ripple level (Preindl and Bolognani, 2011), making them an attractive proposition.

The battery charger, the optional converter that depends on the degree of electrification of the vehicle, interfaces between the electrical grid and the battery in the vehicle. Most of the time, the battery charger steps-down and rectifies the AC voltage to a DC voltage; however, interest is growing in bidirectional topologies, also known as Vehicle-to-Grid (V2G), that allow an unused electric vehicle to supply energy to a load that accepts AC voltage as an input: a house, the power grid, etc. If the charger is on-board as opposed to off-board, then it becomes imperative to reduce its total in-system footprint. If the system is non-integrated, i.e. a separate charging circuit is added, then additional active and passive components are required, which add bulk to the vehicle (Yilmaz and Krein, 2012). WBG materials are favourable to reducing losses and the size of magnetic components. An additional benefit of the employment of WBG semiconductors is that, with a higher efficiency charging system, a battery can be charged faster and, therefore, has the potential to assist in electrified vehicle adoption. Furthermore, if the car is being used in V2G mode, where a bidrectional converter is absolutely necessary, a higher efficiency from the charging circuit would translate in to more energy supplied to the grid, which could assist in grid stability when demand is high.

From this overview of the typical major power converters within an electrified vehicle, two conclusions can be drawn: they need to be small and efficient; and that wide-bandgap materials have the potential to greatly aid in this endeavour. Over the years, many researchers have considered both the efficiency of the individual component and the efficiency of a system when using wide-bandgap transistors. They range in their goals, with some seeking to characterise a device and draw a conclusion and others showing the benefits to be reaped in a particular application.

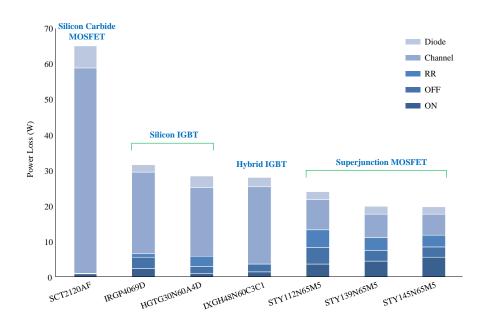

Two studies that consider the first point are (Merkert *et al.*, 2014) and (Jahdi *et al.*, 2014). In both, the authors characterise conventional and Silicon Carbide transistors and make a comparison between the two. In the former, continuous functions for specific devices are built by fitting a curve to the experimentally obtained data and are used for a simulation of an inverter's efficiency. The results showed that an inverter built with Silicon Carbide JFETs performed better than one built with Silicon IGBTs. In the latter study, a Silicon Carbide MOSFET and diode were compared against a Silicon IGBT and diode under several different operating conditions: slew rate, temperature, voltage, current and gate resistance. These results were used for a three-phase inverter conversion efficiency simulation under different modulation schemes. The Silicon Carbide system obtained significantly higher efficiency under different modulation strategies. A third study mapped out the switching and conduction losses of even more switches to come to the same conclusion, although it was published several years earlier (Glaser *et al.*, 2011).

One study published, predating the first two, showed very clearly the gains to be obtained for an electrified vehicle by using Silicon Carbide devices (Zhang *et al.*, 2011) in the inverter stage. The authors experimentally obtained performance curves for a Silicon Carbide JFET and Silicon IGBT for use in simulations of a HEV and PHEV model over a typical driving cycle. The end result was that, in both vehicle architectures, the overall system efficiencies were higher with Silicon Carbide. The resulting junction temperature estimation was low enough that the heatsink could be redesigned and made smaller for the JFET, yielding further synergies.

One drawback to the previous investigation is that it does not take advantage of the higher frequency operation that wide-bandgap semiconductors afford by switching only at 20kHz, nor their ability to operate at higher temperatures than Silicon. These are rectified in (Wrzecionko *et al.*, 2014), where a 10kW inverter operating in an environment with an ambient temperature of 120°C is designed and implemented. Silicon Carbide's maximum permissible junction temperature is higher than that of Silicon, making it favourable for such an application. Replacing a Silicon inverter with the designed one would allow for a reduction in the size and complexity of the heatsink and, consequently, increase the power density of the system.

Another study focused on three converters for automotive applications: one threephase inverter and two DC-DC converters, one bidirectional and the other unidirectional. Using a sample of devices on the market and their ratings, a trend was created to scale devices from one power level to another via die size modifications, with this information being used to develop loss models of the three converters. Under these conditions, all-Silicon Carbide devices offered superior performance to Silicon MOS-FETs, IGBTs and even hybrid Silicon IGBTs, which fuse an IGBT with a Silicon Carbide diode to reduce the reverse recovery losses of the diode when switching. Silicon Carbide MOSFETs were also shown to meet rather handily the demands of the autmotive industry (Biela *et al.*, 2011). Shifting focus entirely to DC-DC converters, a paper published considered an onboard battery charger for an electric vehicle using Silicon Carbide MOSFETs. The topology consists of a boosting rectifier and an isolated step-down converter with a high level of integration and custom-made MOSFET modules. The end result was an on-board charging system outputting just under double the United States Department of Energy's 2022 target, as well as having a power density and specific power five and four times, respectively, larger than the target. No direct comparison is made between Silicon and Silicon Carbide devices, though it can be assumed that the 2010 Prius PHEV that is used as a benchmark did not use WBG materials. In this case, the designed charger achieves much better performance (Whitaker *et al.*, 2014).

The application of wide-bandgap semiconductors is not exclusive to automotive applications. In (Alkayal and Saada, 2013), the researchers designed a three-phase inverter using Silicon Carbide MOSFET modules for an electric train. The main result of the study was that the same techniques for designing a Silicon-based inverter applied to a Silicon Carbide inverter. They also showed that the optimal switching frequency for a Silicon Carbide inverter was higher than that of Silicon, when taking in to account mass, volume and cost of the system. This includes the heatsink and an AC-side filter, which requires inductors and capacitors.

Nor are wide-bandgap materials exclusive to transportation. For photovoltaic applications, the conversion efficiency from panel to grid is of great importance, in no small part due to the fact that solar cells convert a fraction of the energy they receive from the sun. The importance of wide-bandgap materials for these applications was espoused in (Rodriguez *et al.*, 2013) and (Garcia-Rodriguez *et al.*, 2014), with the former considering Silicon Carbide and the latter Gallium Nitride. In both studies,

the efficiency of the wide-bandgap devices are compared with comparable Silicon ones. The results showed clear gains by transitioning to WBG transistors.

An interesting study is undertaken in (Gurpinar and Castellazzi, 2016), where a single-phase T-type inverter is designed using three different switches: a Silicon IGBT, a Silicon Carbide MOSFET and a Gallium Nitride MOSFET. Analysis shows that the GaN FET achieves higher efficiency over temperature, power and switching frequency. This translated in to an estimated reduction in the heat sink size, relative to Silicon Carbide, of almost four times, as well as a lower loss for a given output filter volume, in no small part due to the higher switching frequencies that can be obtained at a lower power loss. The key takeaway is that Silicon Carbide is not the only solution when designing-in wide-bandgap semiconductors and, indeed, niches may exist.

Take, for example, a presentation given by Yole Développement at the Applied Power Electronics Conference (APEC) in 2015 pertaining to market trends in the semiconductor industry. Their statement, concurred with by semiconductor manufacturers, is that different materials will dominate different voltage levels and price points. At the moment, Silicon Carbide and Gallium Nitride are cutting in to highend, performance applications; however, as their cost comes down, they are expected to further erode Silicon's position. Gallium Nitride is expected to be used in ultrahigh frequency applications below 100V and in general converters up to about 600V before Silicon Carbide dominates in higher voltage levels (Gueguen, 2015).

Two papers published using Gallium Nitride hit home its versatility in voltage levels, which is yet to be seen in Silicon Carbide publications where they have so far been used at higher voltage levels. In the first study, Gallium Nitride High Electron Mobility Transistors (HEMTs) are used for a 48 to 12 Volt resonant step-down converter operating at 1.2MHz, delivering several hundred Watts of power. Analytical and experimental results, as well as a low voltage figure of merit (FOM) designed specifically for hard switched GaN devices, show that superior efficiency and performance can be achieved (Reusch and Strydom, 2015).

Similar work on a resonant converter, albeit at a DC bus voltage of 400V, is shown in (Huang *et al.*, 2014). A GaN HEMT is compared with a Silicon MOSFET switching at 1MHz to deliver several hundred watts on a 12V bus. The two share similar conduction losses; however, the switching losses are where the GaN device shines, with a significant reduction exhibited. The end efficiency is several percentage points higher, making it an attractive option for future designs.

In total, the consensus is that wide-bandgap semiconductors are beneficial to loss and system footprint reduction and are worthy of applied research. From this survey of literature, two gaps are observed, both of which are related to the power dense design of a converter: the first is in a simple, accurate and generalised process that does not rely on heavy levels of modelling and testing to preliminarily determine converter losses; and the second is in discrete component selection, where many studies simply state a component was chosen with no process outlined.

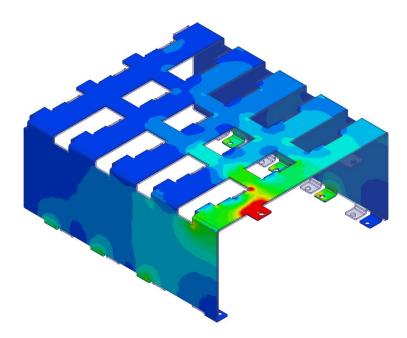

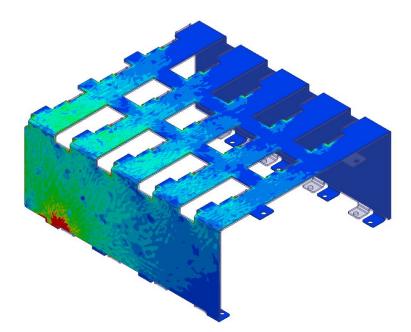

This thesis aims to alleviate these identified issues. In chapter 2, the basics of power semiconductor devices and materials are outlined. Intrinsic material properties show that wide-bandgap semiconductors have inherently great potential to benefit power electronic designs. Figures of merit, for both materials and switches, are presented. For the materials, the benefits to be reaped from moving to designs employing wide-bandgap semiconductors are definitively shown. In chapter 3, a review of modelling techniques is undertaken and a decision is made on which to employ when evaluating the losses of a converter. A three-phase inverter is chosen as the targeted application and the means of evaluating the efficiency are presented. Optimality in component selection, a rarely discussed subject, is introduced, along with several possible approaches. The fundamentals of parasitic parameter analysis of a power transmission system are discussed and exemplified via finite element simulations on a realised bus bar.

Chapter 4 is focussed on the design of the converter, with an emphasis on component selection. The figures of merit for specific devices, introduced in chapter 2, are used to draw an initial conclusion regarding which transistor to use. Simplified analysis under equal operating conditions is used to determine exactly which transistor to design-in as the FOMs are not capable of delivering an exact answer. Novel techniques are used to select the DC-link capacitor, which are equally applicable to any other discrete component selection problem, given appropriate tuning is applied to the data pre-processing and algorithm. The basics of PCB design for a high voltage circuit are discussed and applied to design two versions of the prototype inverter.

Testing of the prototype inverter is presented in chapter 5. The Impedance measurements of a bare board and a populated board show that it is well-designed, exhibiting low parasitic inductance. The inverter is then tested in two configurations, with the first showing good correlation with the basic model at low power and the second showing the temperature of the cases when switching approximately 10.5kW of mechanical power, which translates to roughly 40% of the rated electrical power.

A summary of the work undertaken is given in chapter 6 and potential avenues of future research are outlined.

### Chapter 2

# Switching Devices & Comparative Analysis

#### 2.1 Types of Devices

For electronics applications, there exist many different devices for controlling voltages and the flow of currents. In this section, only the major power switching devices and the basic diode will be discussed to provide the basic framework for moving forward with a comparison of different semiconducting materials and devices for an application.

#### 2.1.1 Bipolar Junction Transistor

The Bipolar Junction Transistor (BJT), invented in the late 1940s, was the first power transistor to have been created and used for power electronic applications.

The most simplified, albeit not fully representative, model of a BJT is that of a

current-controlled switch: a current in the base determines how much current can exit the third terminal of the device. For an NPN BJT, current flows in to the base of the transistor, amplifying the current in the collector; in the case of a PNP BJT, current flows out of the base and determines the amplification in the emitter. The level of amplification is tied to the amplification factor,  $\beta$ , which is dependent upon the doping levels of a specific device. The basic schematic representation is given in Figure 2.1.

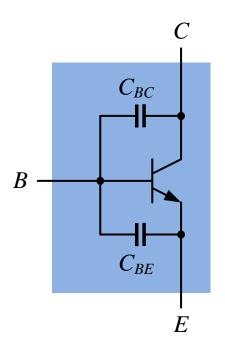

Figure 2.1: BJT schematic with parasitic capacitances.

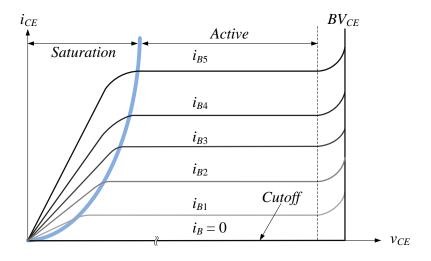

A BJT has three operating modes: cutoff, saturation and active. These can be seen in Figure 2.2. The two modes of interest for a power switch are cutoff and active. Cutoff is achieved when no current is flowing in to or out of the base; active has several conditions that have to be met, which will also determine the flow of current through the device. Coarsely speaking, if a current, i, is defined as positive when flowing from collector to emitter in an NPN BJT,

$$i = \begin{cases} > 0, & \text{if } v_C > v_B > v_E \\ < 0, & \text{if } v_C < v_B < v_E \end{cases}$$

(2.1)

where  $v_C$ ,  $v_B$  and  $v_E$  are the voltages at the collector, base and emitter. For a PNP BJT,  $v_C$  and  $v_E$  would change positions in the inequalities.

Figure 2.2: BJT current-voltage characteristic.

BJTs are minority carrier devices and, as a result, have significant tail currents when turning off due to the need to remove the charge carriers from the base. Moreover, power BJTs often have low current gains and require large base currents to turn on (Mohan *et al.*, 2003). These issues make them unfavourable for high frequency power switching applications due to the significant power losses that can be incurred. BJT relevance is low in modern applications because of MOSFET advances and the introduction of IGBTs, which combine the attributes of a MOSFET and BJT for superior operating characteristics-including an elimination of the base current-and ease of use.

#### 2.1.2 Metal-Oxide-Semiconductor Field-Effect Transistor

The Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) is a voltagecontrolled device where an applied voltage builds an electric field which, when sufficiently high, creates a region where electrons may move through, creating electric current flow. MOSFETs come in two varieties: n-channel (NMOS) and p-channel (PMOS). NMOS devices are preferred due to the higher mobility of the charge carriers, driving a reduction in the on-state resistance for a given die size.

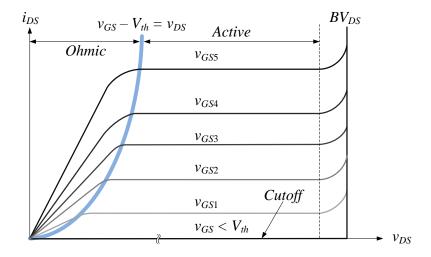

A MOSFET, like a BJT, has three different operational regions: cutoff, triode (or Ohmic) and saturation. The most desirable region to operate in is saturation, particularly for power applications, as it permits a higher current flow with a lower resistance. The three regions are exhibited in Figure 2.3. With the saturation region being of primary interest, it will be the only one to receive discussion. The effects of channel length modulation are omitted.

For a laterally built MOSFET, the current carrying capability of the device in the saturation region can be described as,

$$i_D = \mu_n C_{ox} \left(\frac{W}{L}\right) \left(v_{GS} - V_{th}\right)^2 \tag{2.2}$$

where  $\mu_n$  is the electron mobility  $\left(\frac{cm^2}{V \cdot s}\right)$ ;  $C_{ox}$  is the capacitance of the Silicon dioxide insulation between gate and source and gate and drain;  $\frac{W}{L}$  is the aspect ratio of the

Figure 2.3: MOSFET current-voltage characteristic.

conduction channel, the ratio of the width, W, to the length, L;  $v_{GS}$  is the gate-source voltage applied to the MOSFET; and  $V_{th}$  is the threshold voltage of the device. The product of  $(\mu_n C_{ox}) \left(\frac{W}{L}\right)$  is the channel conductance,  $g_{DS}$ .

This expression is most commonly associated with low voltage MOSFETs for signal amplification purposes as, for power devices, to achieve a sufficient blocking voltage, the length, L, must be increased; however, increasing L drives the channel resistance upwards. There comes a point where the device becomes excessively large and lossy when building laterally. For this reason, power MOSFETs are typically built vertically and are referred to as Diffusion MOS (DMOS) transistors (Sedra and Smith, 2010). Superjunction MOSFETs, described in section 2.3.1, are built using a variation on DMOS techniques.

Despite not being universally applicable to MOSFETs, (2.2) helps with the basic

understanding of a MOSFET's performance. It is also helpful in explaining why Gallium Arsenide devices came to prominence in some applications, despite the bandgap and breakdown electric field strength not being substantially larger than what Silicon offers. A popular means of building Gallium Nitride MOSFETs, which has a much larger bandgap than both Gallium Arsenide and Silicon, is to do so laterally, permitting (2.2) to be employable.

The most basic interpretation of an NMOS is that, under a positive gate-source voltage exceeding the threshold voltage, it is on and under zero (or negative) gatesource voltage it is off. While it is a gross oversimplification, it covers the most important operating characteristics of a MOSFET for power applications. To operate in the saturation region, two conditions must be met:

$$v_{GS} \ge V_{th} \tag{2.3a}$$

$$v_{GS} - V_{th} \ge v_{DS} \tag{2.3b}$$

wherein  $v_{DS}$  is the drain-source voltage, which is the drain-source current,  $i_{DS}$ , multiplied with the on-state resistance,  $r_{DS}$ .

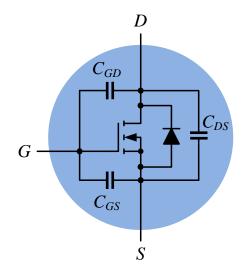

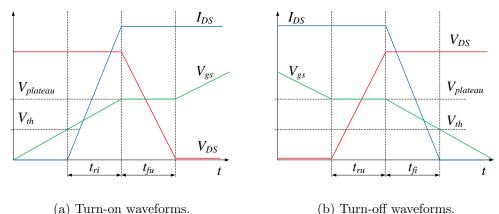

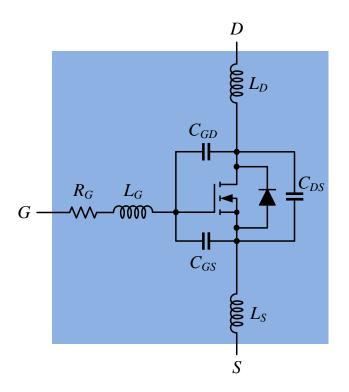

A schematic representation of a typical MOSFET with its parasitic capacitances is given in Figure 2.4. When switching a MOSFET, the parasitic capacitances contribute greatly to its performance. The two that contribute most significantly are  $C_{iss}$ and  $C_{rss}$ , which affect the current and voltage transition times, respectively. They are defined as,

$$C_{iss} = C_{GS} + C_{GD} \tag{2.4}$$

$$C_{rss} = C_{GD} \tag{2.5}$$

where  $C_{GD}$ ,  $C_{GS}$  and  $C_{DS}$  are the gate-drain, gate-source and drain-source capacitances, respectively.

Figure 2.4: MOSFET schematic with parasitic capacitances.

Contributing to the overall energy losses of the MOSFET is the equivalent output capacitance,  $C_{oss}$ . It can be calculated as (2.6).

$$C_{oss} = C_{DS} + C_{GD} \tag{2.6}$$

Together, the capacitances and resistance fully describe a given MOSFET. Under specific operating conditions, the switching transition times can be approximated and, thusly, the losses. MOSFETs find the most use in lower voltage, lower current, high frequency applications.

# 2.1.3 Insulated-Gate Bipolar Transistor

The Insulated-Gate Bipolar Transistor (IGBT) is the combination of both a MOSFET and BJT in a single semiconductor structure. An IGBT is built vertically in the same fashion as a DMOS with an additional p layer added, which gives rise to a pn junction that forms the BJT. Schematics of the device can be seen in Figure 2.5, where (a)is the more comprehensive-yet approximated-internal model of an IGBT and (b) is the most basic representation, where it is considered simply as a voltage-controlled device.

The IGBT is composed of two stages: a PNP BJT that conducts current and the

n-channel MOSFET that controls its base and, hence, the flow of current. When the gate of the NMOS is driven high and it turns on, the base of the PNP is permitted to conduct current from Base to Emitter, giving rise to a voltage,  $v_{BE}$ , that influences how much current flows from Collector to Emitter.

In reality, the top terminal of a PNP BJT is the Emitter and the bottom the Collector, which does not match the schematic representation of Figure 2.5; however, since it acts like an NPN BJT where it conducts with a positive applied voltage, the notation of Collector on top and Emitter on the bottom avoids confusion in practice. This discussion is relevant for an n-type IGBT. Its current-voltage characteristic is more or less equivalent to that of a MOSFET.

The IGBT, like the BJT, suffers from long tail currents when switching off due to its minority carrier structure. This makes it unfavourable for high frequency applications as the off-switching energy is high; however, the base current required to drive the device is eliminated, making it much better for use than a BJT. IGBTs find widespread use in high voltage, high current, low frequency converters.

# 2.1.4 Hybrid Silicon

Hybrid Silicon devices combine Silicon and Silicon Carbide components within the same package. This normally entails the use of a Silicon device as the switch, either a MOSFET or an IGBT, with the freewheeling diode being Silicon Carbide. However, since a MOSFET has a parasitic diode embedded in its structure, the benefits to be seen by paralleling a separate diode are more evident with respect to conduction and not switching. The total gains are more pronounced with IGBTs and, as a result, the majority of commercially available hybrid Silicon devices are Silicon IGBTs copackaged with Silicon Carbide diodes. This allows these hybrid transistors to mesh the superior current carrying characteristics of an IGBT with the reduced reverse recovery losses of a Silicon Carbide diode. This provides a strong benefit when considering high voltage, high current devices, as the reverse recovery energy is linked intrinsically to the junction capacitance of the diode which, itself, grows with the demanded blocking voltage.

A typical schematic for a hybrid IGBT is shown in Figure 2.6. The sole point of differentiation between a hybrid IGBT and a standard IGBT is the inclusion of a Silicon Carbide freewheeling diode.

Figure 2.6: Hybrid IGBT schematic with parasitic capacitances.

Hybrid IGBTs find use in the same circuits that regular IGBTs do. The lower losses associated with the Silicon Carbide freewheeling diode can enable a reduction in heatsink size or an increase in the switching frequency of the converter.

### 2.1.5 Diodes

Diodes, in contrast to the other devices discussed so far, are two terminal semiconductors that only permit unidirectional current flow. BJTs, MOSFETs and IGBTs permit bidirectional flow by controlling whether the device is on or off via a third terminal, making them inherently more versatile.

The most basic model of a diode is a unipolar switch that turns on when the voltage applied to the anode is higher than the minimum voltage drop on the junction,  $V_F$ . When this condition is met, current flows from anode to cathode; if not, then no current may pass.

The current-voltage characteristic of a typical diode is shown in Figure 2.7. The forward voltage is non-linear and is a function of the current being passed by the device. Once a minimum voltage,  $V_j$ , is surpassed on the anode, current begins to flow from anode to cathode.

Figure 2.7: Current-voltage characteristic of a generic diode.

Diodes find widespread use in power converters, as they provide a path for energy stored in parasitic parameters and inductances to be dissipated. Without an anti-parallel (or freewheeling) diode, the voltage would rise until the semiconductor device is forcibly short-circuited. Depending on the circuit topology and efficiency requirements, diodes can be replaced by tightly-controlled transistors acting in an identical manner.

# 2.2 Why Consider Wide-Bandgap Materials?

Wide-bandgap materials have many properties that are beneficial to power electronic applications. The larger bandgap itself gives rise to many of them: high temperature operation, radiation hardening, high blocking voltage and lower total power losses.

The simplest model of a semiconductor is that there exist three regions: the valence band, which is where the electrons rest until excited; the conduction band, which is where electric current begins to flow as the movement of electrons; and the bandgap, the region separating the two. As one would expect, as the bandgap grows larger, so, too, does the amount of energy required to excite electrons to jump from the valence to conduction band. This is the reason why wide-bandgap materials have some of their beneficial properties. In terms of radiation hardening, significantly more energy is required to force turn-on from an external source. For high temperature operation, more thermal energy is required to excite the electrons in the valence band sufficiently to make the transition. For the blocking voltage, a higher electric field is required to cause dielectric breakdown and force conduction. Together, these allow wide-bandgap materials to perform in harsher environments.

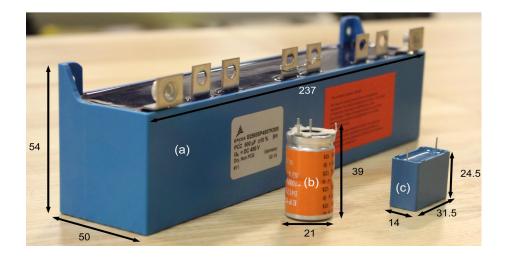

Related to the bandgap are the power losses of a device. As will be discussed in section 2.3.5, the internal capacitances and resistances of a MOSFET can be determined from the semiconducting material's properties. Wide-bandgap materials allow for lower resistances and capacitances to be achieved for a given blocking voltage capability, thereby reducing the losses under all operating conditions. Reduced capacitances, in turn, allow for the switching frequency to be increased, driving a reduction in the size of certain passive components: capacitors, inductors and transformers. Several capacitors for power electronic applications are shown in Figure 2.8. Capacitor (b), were it rated for 800V, would likely be larger than (a); conversely, if capacitor (c) were to have a capacitance of  $1000\mu$ F, it, too, would be large. In reducing the capacitance requirements for a given voltage ripple, the size of a converter can be decreased dramatically.

Figure 2.8: DC capacitors of different types, voltages and capacitances: (a) 400V,  $500\mu$ F, film; (b) 63V,  $1000\mu$ F, electrolytic; and (c) 800V,  $5\mu$ F, film.

These, among other reasons (Gueguen, 2015), are why wide-bandgap materials are finding increasing usage in industry and academia.

# 2.3 Types of Semiconductor Materials

There are many possible semiconducting materials for electronics applications; however, only a few of them show good promise, as well as being commercially viable now or in the future, near or far. Properties key to electronics applications for these elements are provided in Table 2.1. An individual treatment of each material follows in the proceeding sections.

| Material             | $E_g$ | $\epsilon_r$ | $E_c$  | $\mid \mu_n$ | $\mid \mu_p$ | $\mid \lambda$ | $\nu_{sat}$ |

|----------------------|-------|--------------|--------|--------------|--------------|----------------|-------------|

| Si                   | 1.12  | 11.9         | 300    | 1500         | 600          | 1.5            | 1           |

| GaAs                 | 1.43  | 13.1         | 400    | 8500         | 400          | 0.46           | 1           |

| 6H-SiC               | 3.03  | 9.66         | 2500   | 400          | 101          | 4.9            | 2           |

| 4H-SiC               | 2.36  | 10.16        | 2200   | 1000         | 115          | 4.9            | 2           |

| $\operatorname{GaN}$ | 3.45  | 9            | 2000   | 1250         | 850          | 1.3            | 2.2         |

| Diamond              | 5.45  | 5.5          | 10,000 | 2200         | 850          | 22             | 2.7         |

Table 2.1: Semiconductor material properties (Tolbert *et al.*, 2003).

The parameters in Table 2.1 are: the bandgap,  $E_g$  (eV); the relative dielectric constant,  $\epsilon_r$ ; the critical electric field,  $E_c$  (kV/cm); the electron mobility,  $\mu_n$  ( $\frac{cm^2}{V \cdot s}$ ); the hole mobility,  $\mu_p$  ( $\frac{cm^2}{V \cdot s}$ ); the thermal conductivity,  $\lambda$  ( $\frac{W}{cm \cdot K}$ ); and the saturated electron drift velocity,  $\nu_{sat}$  (×10<sup>7</sup>cm/s).

# 2.3.1 Silicon

Silicon is ubiquitous and is synonymous with the modern world. It has been the workhorse of electronics since transistors began to supersede vacuum tubes in the 1950s, beginning first with BJTs and now progressing steadily with MOSFETs and IGBTs. However, it is beginning to approach its theoretical limits in terms of  $R_{DS(ON)}$ and internal capacitances, making gains increasingly incremental. Innovations in manufacturing and structure are being used to try to alleviate this (Brown, 2006). One such example is the Superjunction MOSFET.

#### Silicon Superjunction

Silicon Superjunction (SJ) MOSFETs are amongst the latest advancements in Silicon MOSFET technology. Superjunction MOSFETs change the physical build of a device: instead of a strict vertical structure where thicker layers are required to block higher voltages, the idea of charge balancing is employed to cancel electric fields under reverse bias conditions, thereby reducing the necessary layer thickness to block a given voltage (Havanur and Zuk, 2015). The largest benefits are a lower gate capacitance–and, consequently, gate charge to fully turn on–and a lower  $R_{DS(ON)}$  per unit area than standard Silicon. These features enable higher frequency, higher power operation of a MOSFET in the same package, thereby providing the opportunity to increase the efficiency and power density of a converter.

# 2.3.2 Silicon Carbide

Silicon Carbide (SiC) is one of the current most promising novel semiconductor materials for high power switching applications. A Ph.D thesis was written on the systemlevel benefits it could provide (Ozpineci, 2002) and the results were overwhelmingly positive, even with few MOSFETs and primarily low voltage, low current SiC diodes available. Further research has been conducted as the technology has matured and the offerings widened that continued to show strong gains.

Silicon Carbide has many polytypes; however, the two most widely available for power devices are 4H and 6H, with 4H being the polytype of choice (Tolbert *et al.*,

2003). SiC, resulting from its material properties (see Table 2.1), outperforms basic Silicon in a die of the same size both electrically and thermally. It exhibits a lower on-state resistance, blocks a higher voltage per unit area and has significantly reduced switching energies due to the smaller die structure while also evacuating heat more efficiently than Silicon; however, current packaging and bonding materials limit the recommended maximum junction temperature. Solutions are currently being devised (Horio *et al.*, 2012) so as to take advantage of its ability to operate at very high junction temperatures and eclipse Silicon in another regard.

# 2.3.3 Gallium Nitride

Gallium Nitride is the other semiconductor technology that has been gaining increasing attention. Its properties are favourable–more so than Silicon Carbide–to reducing switching losses. Lateral device structures, where current flows horizontally as opposed to vertically, have also helped in driving down the on-state resistance and the capacitances that contribute to switching losses. Research has shown solid leaps over Silicon performance (Reusch and Strydom, 2015,?; Huang *et al.*, 2014) and, even, over Silicon Carbide MOSFETs (Gurpinar and Castellazzi, 2016). GaN shows promise for high and low power switching applications.

Gallium Nitride devices are often referred to as High Electron Mobility Transistors (HEMTs) as a result of their high electron mobility parameter. To date, significant work has been done to design normally-off devices as opposed to normally-on. Two of the major approaches to developing an enhancement mode (normally-off) device are the cascode structure, where an enhancement mode Silicon MOSFET is placed in series with the GaN FET and gate doping, to achieve a positive threshold voltage (Jones *et al.*, 2014).

## 2.3.4 Gallium Arsenide

Gallium Arsenide (GaAs) has seen use for some time in radio frequency applications. The small increase in bandgap relative to Silicon makes it less susceptible to accidental turn on due to radiation and, thus, it has been favoured for aerospace and satellite designs. The high electron mobility reduces the dynamic channel resistance of a GaAs MOSFET and, even though the relative dielectric constant is higher than Silicon, the increase in switching losses associated with a higher capacitance can be mitigated by taking advantage of the higher critical electric field, enabling a smaller die to be used and an overall lower capacitance achieved. An additional benefit of the reduction in the on-state resistance is that there is an increase in the cutoff frequency of the device, allowing GaAs MOSFETs to operate over a wide frequency band without suffering significant attenuation (Ajram and Salmer, 2001).

With respect to power electronic applications, GaAs is not widely used. Indeed, its low thermal conductivity makes evacuating heat a challenge. With junction temperature being the limiting factor of power switches, Gallium Arsenide devices are unable to sustain large power losses without significant and complex cooling solutions added. These issues do not preclude GaAs transistors from being used for power switching applications. Some research has been done–one example being (Ajram and Salmer, 2001)–that shows them as low voltage power switches; however, they are unlikely to gain much traction with the advent of Gallium Nitride devices that are superior in many regards. It is more probable that Gallium Nitride will cut in to applications that Gallium Arsenide currently holds.

# 2.3.5 Examples

To illustrate the benefits of wide-bandgap semiconductor materials, several important parameters related to devices used in switching applications will be introduced and elaborated upon.

The specific on-resistance is defined by (2.7). It is also referred to as the drift region resistance and, for high voltage MOSFETs, it dominates the total on-state resistance of the device (Mohan *et al.*, 2003; Havanur and Zuk, 2015). Thus, minimising  $R_{on,sp}$  is an important part of driving efficiency higher. It can be clearly observed that a high permittivity, mobility and critical electric field are beneficial to this task. Referring back to Table 2.1, it becomes obvious that wide-bandgap materials are key to this endeavour.

$$R_{on,sp} = \frac{4V_B^2}{\epsilon\mu E_c^3} \tag{2.7}$$

An alternative means of quantifying the resistance is given by (2.8), which is the calculation of the resistivity of a sheet of semiconducting material in its most fundamental sense. In this case, a low resistivity is desired. This is achieved by driving the doping concentrations and mobilities of electrons and holes higher. Silicon, as a whole, tends to have higher mobilities, which favour it for a given doping density; however, wide-bandgap materials allow for higher doping to be achieved because of their higher critical electric fields and relative permittivities. Hence, when considering all factors, wide-bandgap materials can still achieve lower resistances than Silicon, per the definition of the resistivity of a semiconductor,

$$\rho = \frac{1}{q\left(N_n\mu_n + N_p\mu_p\right)} \tag{2.8}$$

where q is the value of an elementary charge and  $N_n$  and  $N_p$  are the doping densities of electrons and holes, respectively.

To help make this point, consider a simple pn diode. Its blocking voltage can be approximated as (2.9) (Mohan *et al.*, 2003),

$$V_B \approx \frac{\epsilon_r E_c^2}{2qN_d} \tag{2.9}$$

where  $N_d$  is the total doping density. For wide-bandgap materials, their numerators are significantly larger than the numerator for Silicon. The consequence of this, under equal doping levels, is a heightened blocking voltage. However, as previously discussed, the doping level is inversely proportional to the resistivity. Thus, in achieving the same blocking voltage, wide-bandgap diodes have lower resistances.

Observing the dependency of the blocking voltage on the doping of the material, a relationship can be envisioned with (2.7) in mind: as doping increases,  $V_B$  drops and, consequently, the specific on-state resistance of a MOSFET. Great benefit can be observed by pushing the doping concentration up to a certain level to achieve a desired blocking voltage.

Continuing in this vein, the specific input and output capacitances per unit area can be calculated using material parameters. They are given by (2.10) and (2.11), respectively,

$$C_{iss,sp} = \frac{\epsilon E_c}{2\sqrt{V_G V_B}} \tag{2.10}$$

$$C_{oss,sp} = \frac{\epsilon E_c}{2\sqrt{V_D V_B}} \tag{2.11}$$

where  $V_G$  and  $V_D$  are the voltages applied to the gate and drain, respectively, of the

#### MOSFET.

The results in table 2.2 indicate that wide-bandgap materials will have a higher specific input and output capacitance. However, it should be noted that the specific capacitances are measured in Farads per unit area. Wide-bandgap devices, relative to their Silicon counterparts, require a smaller area to block the same voltage and, hence, their capacitances will be lower. Indeed, in calculating the depletion width, this can be shown.

$$W_d = \frac{2V_B}{E_c} \tag{2.12}$$

The depletion width can alternatively be represented as,

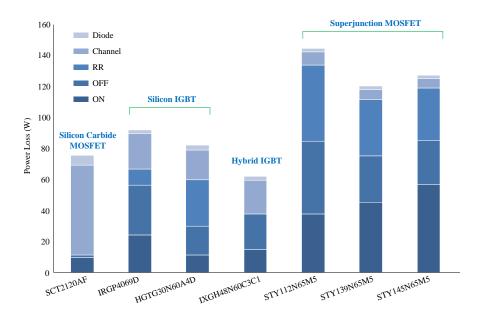

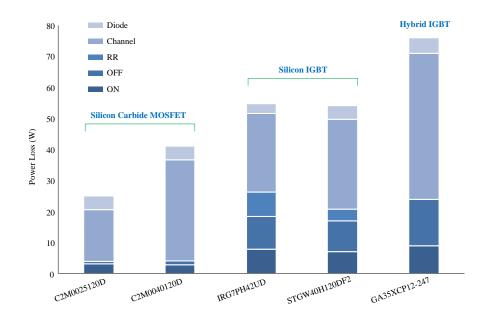

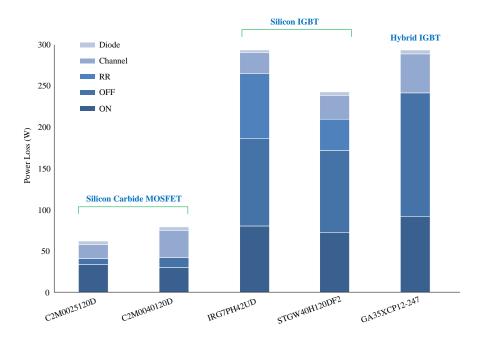

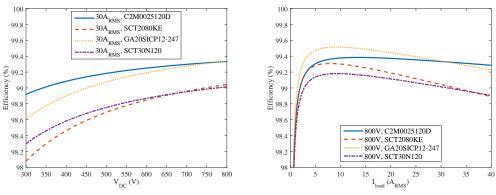

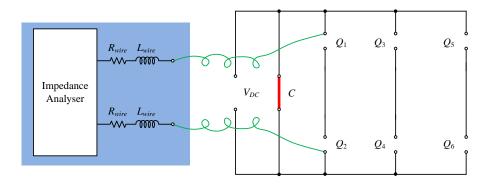

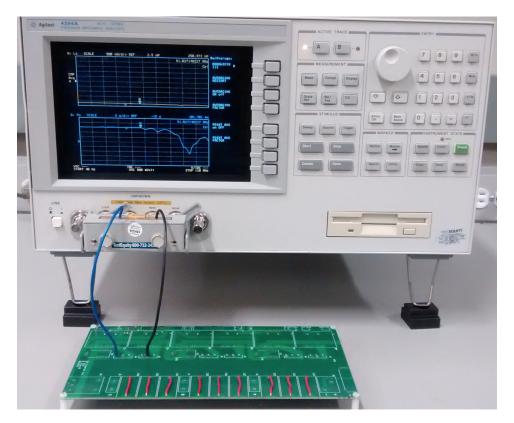

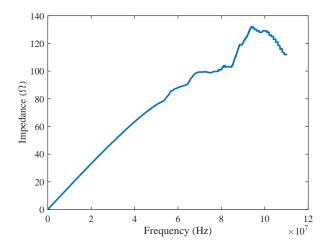

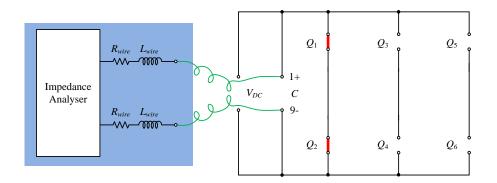

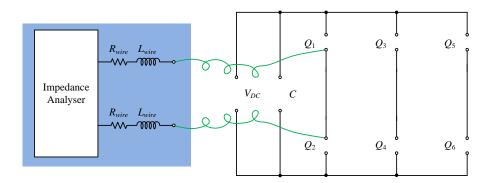

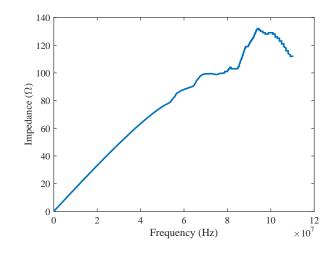

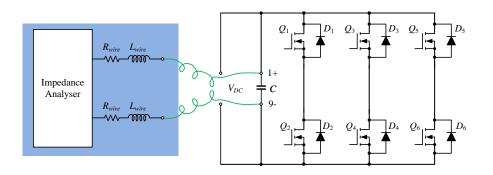

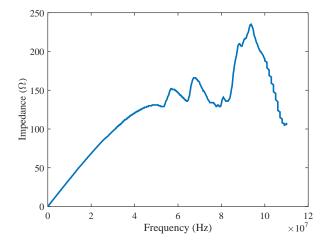

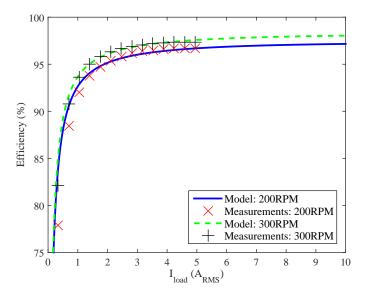

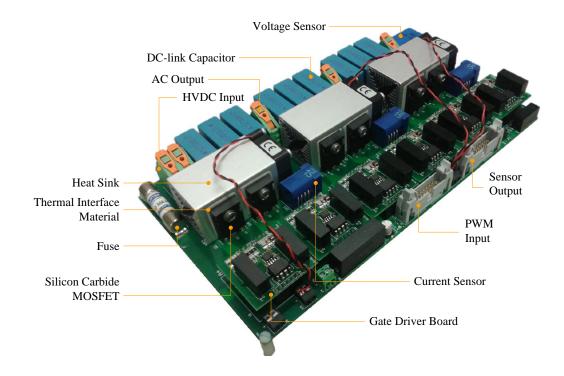

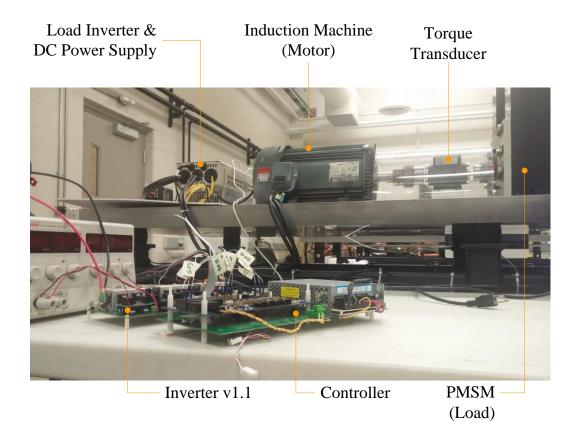

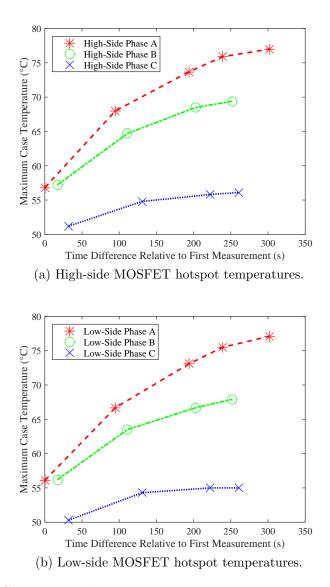

$$W_d = \sqrt{\frac{2\epsilon V_G}{qN_d}} \tag{2.13}$$